APPLICATION NOTE

# Binning Mode Operation of 20 and 24 Micron Pixel Full Frame CCD Sensors

September 10, 2003 Revision 1.0

#### **TABLE OF CONTENTS**

| INTRODU              | CTION                                                                              | 3      |

|----------------------|------------------------------------------------------------------------------------|--------|

| SENSOR               | OPERATION                                                                          | 3      |

| IMAGE A              | CQUISITION                                                                         | 3      |

| VERTICA              | L REGISTER OPERATION                                                               | 3      |

| BINNING              | VERTICALLY                                                                         | 3      |

| HORIZON              | TAL REGISTER OPERATION                                                             | 3      |

| STANDA               | RD HORIZONTAL OPERATION                                                            | 3      |

| HORIZON              | TAL BINNING                                                                        | 6      |

| Genera<br>Horizo     | AL PRINCIPAL OF HORIZONTAL BINNING                                                 | 6<br>6 |

| PIXEL SA             | TURATION: NOMINAL CCD SETTINGS                                                     | 10     |

| PIXEL SA             | TURATION: ADJUSTED CCD SETTINGS                                                    | 13     |

| SATURAT              | ED VIDEO OUTPUT SIGNAL                                                             | 14     |

| BIAS REC             | OMMENDATIONS WHEN BINNING                                                          | 16     |

| SIIMMAD              | Υ                                                                                  | 17     |

| LIST OF F            |                                                                                    |        |

| Figure 1             | Normal readout through low gain output                                             | 4      |

| Figure 2<br>Figure 3 | Normal vertical clock timing  Vertical timing to combine two lines                 |        |

| Figure 4             | Normal pixel rate timing.                                                          |        |

| Figure 5             | Two columns combined (binned) on to the floating diffusion                         |        |

| Figure 6             | Two columns combined (binned) on to the floating diffusion (small signal)          |        |

| Figure 7             | Figure 7 Two columns combined (binned) on to the floating diffusion (small signal) |        |

| Figure 8             | Two columns binned on to H21 (Sample/Clamp/Vid)                                    |        |

| Figure 9             | Two columns binned on to H21 (H1, H21, Reset)                                      |        |

|                      | Two columns binned on to H21 (Video,H21,clamp clock)                               | 9      |

| Figure 11            | Charge Transport: 2X2 Binning On Floating Diffusion Using Low Gain (2µV/electron)  | 0      |

| Figure 12            | Output                                                                             |        |

| Figure 13            | · · · · · · · · · · · · · · · · · · ·                                              |        |

| Figure 14            | Floating Diffusion Charge Capacity (Nominal Settings)                              |        |

|                      | Floating Diffusion Capacity after VRD, VOG, Reset Adjustments                      |        |

|                      | Output video when charge flows back over the output gate                           |        |

| Figure 17            | Charge Flowing back over VOG when the outhe floating diffusion capacity is reached |        |

| Figure 18            |                                                                                    |        |

| Figure 19            | Charge lost over the Reset Gate                                                    | 15     |

#### Introduction

This application note is intended to describe two methods for operating Kodak's  $20\mu m$  and  $24\mu m$  Pixel Full Frame CCD sensors when binning is desired. The note gives a detailed explanation of both methods and associated performance issues.

The applicable CCD sensors include:

- KAF 0261E (20µm x 20µm pixels)

- KAF 1001E (24µm x 24µm pixels)

- KAF 4301E (24µm x 24µm pixels)

#### **Sensor Operation**

#### Image Acquisition

An electronic representation of an image is formed from a CCD image sensor when incident photons falling on the CCD active area create electron-hole pairs within the device. These photon-induced electrons are collected locally by the formation of potential wells at each photo gate or pixel site. The number of electrons collected is linearly dependent on light level and exposure time and non-linearly dependent on wavelength.

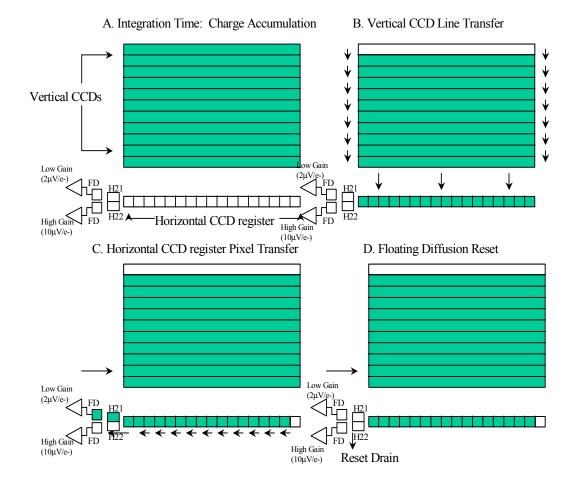

After the CCD has been illuminated, the charge accumulated in the pixel sites is clocked out of the sensor in a two-step process. operating in a normal, or non-binning, mode, a single line (row) of charge is first shifted out of the vertical CCD array and into the horizontal CCD register in parallel. The line of charge is then serially shifted toward the floating diffusion (FD) output node by the horizontal register. Before reaching the floating diffusion node the charge passes over the last cell of the horizontal register known as the transfer gate (TG; 20µm and 24µm devices only). The H21 and H22 clock inputs play this role on Kodak full frame sensors. These gates are separate from the rest of the horizontal register and direct the charge to the desired output node. Each pixel's charge is then converted into a voltage and is sensed off chip. After the CCD output signal has been sampled by the system electronics, the charge on the floating diffusion is removed via the Reset Drain (VRD) by action of the Reset Clock. The floating diffusion is reset to the potential applied to VRD. This is repeated for all succeeding pixels in the line, and lines in the array (see Normal readout through low gain Figure 1 output).

#### **Vertical register operation**

#### **Binning Vertically**

When operating the CCD sensor in vertical binning mode, two or more lines of charge are combined together in the horizontal CCD register, before the horizontal clocks begin to shift the charge towards the floating diffusion output node. This charge is shifted to the output, pixel by pixel, in a manner identical to normal operation. In order to accomplish rowsummation, the horizontal register is designed with a significantly larger capacity than the vertical register so that more than one row can be combined and read out.

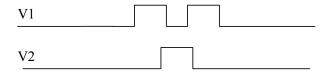

In normal mode operation the Vertical Clocks V1 and V2 shift lines of charge into the horizontal CCD register in parallel, while H1 is held high and H2 is held low. The clocking sequence for a full frame sensor is shown in Figure 2. On the rising edge of V2, the line of charge in the last Vertical CCD line is transported into the Horizontal CCD register.

When operating the CCD in a binning mode, an additional sequence of the V1 and V2 clocks is repeated for as many times as the binning mode dictates before beginning to clock the charge out of the horizontal CCD register. A vertical register timing scheme for binning 2 rows is shown in Figure 3. Two lines of charge would be transported onto the Horizontal CCD register.

#### Horizontal register operation

#### **Standard Horizontal Operation**

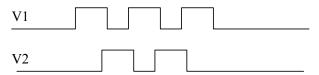

The floating diffusion is the structure on CCDs that exists between the input of the on-chip amplifier and last phase of the horizontal register. This structure is responsible for summing the electrons from each pixel and presenting it as a voltage to the input gate of the output amplifier. The reference voltage, or "zero state" of the floating diffusion is set to VRD when the Reset clock goes high. This effectively sets the offset voltage of the output video. The

output video stays at this voltage until H22 or H21 pulses low (H1 subsequently moves high) forcing a new packet of electrons onto the floating diffusion. H22 and H21 act as steering versions of the H2 register. Electrically separated from H2, H21 and H22 are used to select which output amplifier will be used to read voltages from the device. If a low gain operation is desired, H21 is chosen to mimic H2, and H22 is set slightly more negative than H21-Low. In this mode all charge is transferred to the floating

diffusion that is attached to the low gain amplifier (amp1). For high gain operation the roles of H21 and H22 are reversed from the above description. Normal mode horizontal clocking is shown below in Figure 4.

Figure 1 Normal readout through low gain output

Figure 2 Normal vertical clock timing.

Figure 3 Vertical timing to combine two lines.

Figure 4 Normal pixel rate timing.

#### **Horizontal Binning**

## General Principal of Horizontal Binning

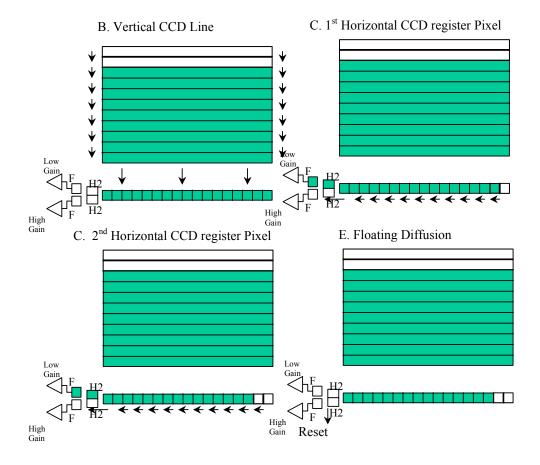

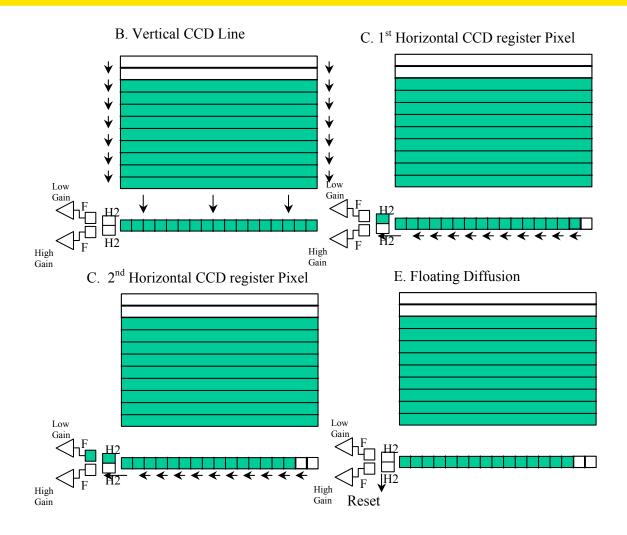

In order to operate in horizontal binning mode, charge from the horizontal register must be summed at or before the input of the output amplifier. On the Kodak 20µm and 24µm pixel devices there are two ways to accomplish this. One method is to sum the charge on the floating diffusion by sending the reset pulse every other pixel period. This method of binning may be implemented on every Kodak full frame CCD. The other method is to sum charge on the H21 or H22 transfer gates, effectively using them as a summing gate. The later method allows the clamp and sample pulses to be temporally identical to normal mode timing, allowing for a noise performance that is more comparable to normal mode operation

### Horizontal binning on to the floating diffusion

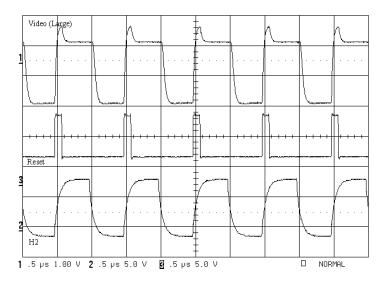

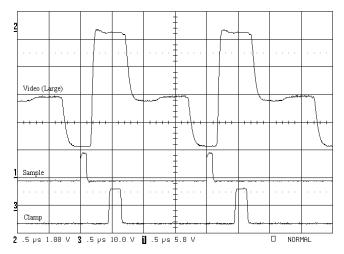

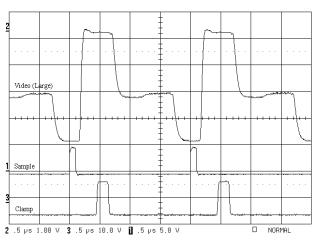

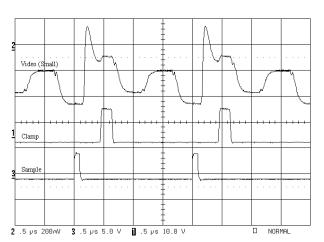

CCD Timing for horizontal binning operation where charge is to be collected on the floating diffusion is similar to the standard method of clocking with the exception of the reset clock. For charge to be collected on the floating diffusion, rather than resetting the FD back to VRD every cycle, charge is allowed to accumulate for as many cycles as desired. Figure 7 shows the reset clocking required to bin two columns on the floating diffusion. Note that video signal mirrors the H2 clock in its appearance for low signal operation but the effect is much less when larger signals are being read out. This is because the H2 signal capacitively couples into the output. Although visible in the waveform this does not affect the amount of signal being read by the output amplifier. Figures 5 and 6 also show the positions of clamp and sample pulses. From these figures it can be observed that the sample pulse is nearly 3/4 of a binned period from the clamp pulse. decreases the effective sampling frequency of the CDS (Correlated Double Sampling circuit) and may lead toward increased temporal noise in some systems.

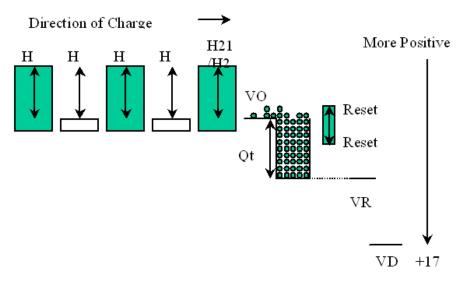

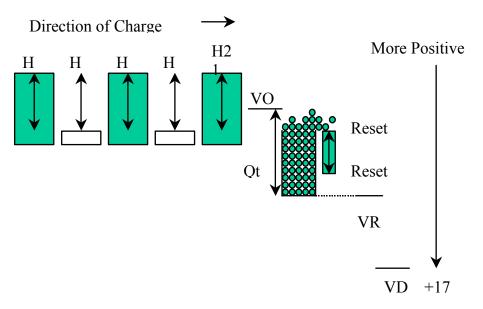

## Horizontal Binning with Transfer Gates

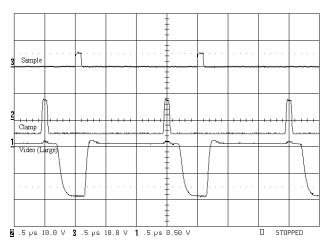

In order to reduce noise susceptibility when binning horizontally, many CCD manufactures will have a binning gate or "binning well". This is a single cell of the horizontal register located at the output end of the register that is electrically separated from the rest of the horizontal register. This separation allows for it to be clocked independent of the rest of the register and enables charge to be summed within the cell before it is transferred to the floating diffusion. The Kodak large pixel devices have a similar signal phase gate of the horizontal register that is electrically isolated from the rest of the register. This gate is the transfer gate, H21 or H22. The primary function of this gate is to steer charge to one of the two on-chip output amplifiers. In normal mode operation for high gain performance H22 is clocked identically to H2 while H21 is held low. Likewise, for standard low gain operation H21 is clocked identically to H2 while H22 is held low. Charge is accumulated in the transfer gate when it is in a high state and shifted when the signal moves more negative. In order to accumulate charge on the H21 or H22 transfer gate, (H21 is typically used since the low gain amplifier has a higher dynamic range) negative going phases of H21 or H22 are removed for each cycle that

binning is desired. The benefit of this method of operation is that charge is transferred once onto the floating diffusion during ½ of the standard pixel The time between clamp and sample pulses with this mode is the same as in normal operation allowing for the same performance calculations to apply in binning mode that applied in standard mode. Figures 8 through 10 show the timing modifications and resulting video. H22 is assumed to be held at a DC state that is more negative than H21-Low, and all timing that is not shown in the figures is unaltered. The caveat to this method of binning is that the capacity of the horizontal register is appreciably less than the capacity of the low gain output amplifier. When binning on the floating diffusion the only charge limit is the output amplifier and the electrostatic potentials surrounding the floating Conversely, when binning on the transfer gate the primary limiting factor is the capacity of the summing gate (same as horizontal register). In the case of Kodak's 24µm and 20µm pixel CCD devices, the charge capacity of the summing gate is less than that of the floating diffusion and output amplifier (see table 3 and figure 13).

Figure 5 Two columns combined (binned) on to the floating diffusion

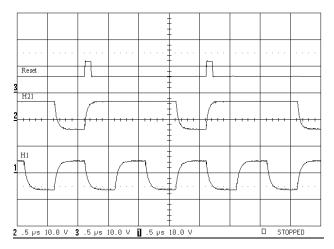

Figure 7 Figure 7 Two columns combined (binned) on to the floating diffusion (small signal)

Figure 6 Two columns combined (binned) on to the floating diffusion (small signal)

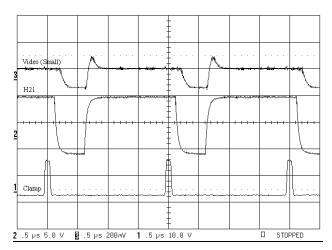

Figure 8 Two columns binned on to H21 (Sample/Clamp/Vid)

Figure 9 Two columns binned on to H21 (H1, H21, Reset)

Figure 10 Two columns binned on to H21 (Video,H21,clamp clock)

Figure 11 Charge Transport: 2X2 Binning On Floating Diffusion Using Low Gain (2μV/electron) Output

Figure 12 Charge Transport: 2X2 Binning On Transfer Gate (H21) Using Low Gain (2μV/electron) Output

# Pixel Saturation: Nominal CCD settings

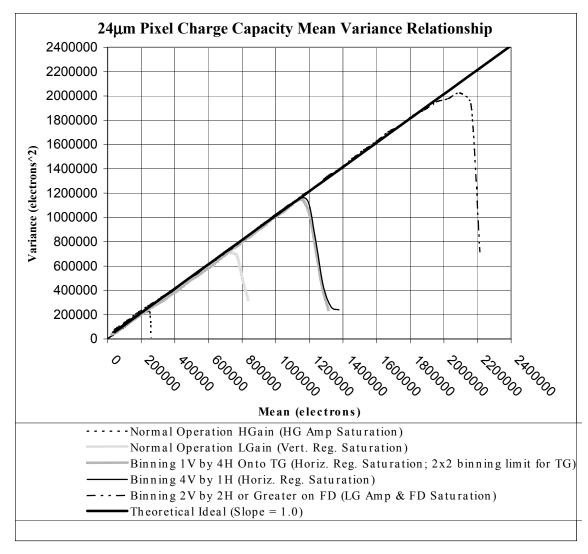

The 20µm and 24µm pixel devices have saturation levels that vary according to the mode of CCD operation. See Figure 13 for details. When operating a 24 µm Pixel KAF-Series CCD through the high gain output amplifier with the nominal settings as dictated in the Device Specifications Sheet, the output amplifier will fail first at 200,000 electrons. The full dynamic range of these devices operating in normal mode can be achieved using the low gain output amplifier. In normal mode operation using the low gain output amplifier, the first CCD structure to reach capacity as illumination is increased are the vertical registers. When this occurs streaks

and column defects will appear in the image as individual vertical registers saturate. With 24µm pixel devices this occurs at an exposure of approximately 650 electrons. Figure 13 shows the charge capacity measurement using the Variance vs. Mean technique. This technique leverages the Poisson behavior of electron noise (shot noise). According to this behavior the shot noise component of the variance must equal the mean where the units of measure are electrons squared and electrons respectively. Since shot noise is the only noise component that increases with increasing signal, the slope of a Mean vs. Variance plot is always equal to 1.0 as long as the CCD is operating properly. This relationship is only true if both the mean and standard deviation are plotted in electrons. If the units are

not plotted in electrons, the slope of the nonelectron units curve will provide a system conversion factor to electrons. When an element or elements of a CCD begin to fail due to saturation the first sign of failure is a deviation from the mean variance relationship. Saturation causes charge to blend with adjacent pixels, forces charge to leak to adjacent structures, or quantizes the conversion of charges packets. In any case, saturation causes the measured Mean vs. Variance data to fall away from the ideal slope of 1.0. The mean value at which the deviation begins to increase with increasing signal is the charge capacity of the CCD under those particular operating conditions. Through the use of this plotting technique under various operating conditions and modes, different internal structures within the CCD can be made to fail according to the Mean vs. Variance plot. In this method charge capacities for the various structures within a CCD can be determined.

The large pixel Kodak CCDs may operate in binning mode on both the low gain and high gain outputs. However, binning on the high gain output will not increase the maximum output signal since the amplifier itself saturates at 2 volts. On a positive note, the high gain amplifier may be used in combination with a binning mode clocking scheme when maximum sensitivity is desired with relatively low noise. With this configuration any bright points or hot spots in the image that produce more than 200,000 electrons inside the CCD will be

absorbed by the excess dynamic range of the vertical and horizontal registers and will be clipped by the output amplifier without damaging the rest of the image. This method of operation uses the dynamic range of the internal CCD structures as a means of blooming suppression.

The horizontal registers in Kodak's scientific CCDs are designed to have nearly twice the electron capacity per cell as the vertical registers. This allows for binning in the vertical direction of 2 rows without saturation of the horizontal register. In 24µm pixel devices the horizontal register has a charge capacity of 1,100,000 electrons, while the vertical registers have a capacity of 650,000 electrons.

When binning 2 vertical by 2 horizontal the charge capacity in terms of the structural limits of the main horizontal and vertical registers should be 2,200,000 electrons for a 24µm pixel device. This is slightly larger than the maximum achievable capacity through the low gain amplifier when binning 2x2 on the floating diffusion, which has a maximum linear capacity of 1.9 million electrons. Therefore, the effective capacity of the CCD as a whole is 1.9 million electrons. However, this does allow for a wellbalanced binning of nearly 4 volts of signal. On the other hand, if the transfer gate is used for binning instead of the floating diffusion, the maximum attainable charge output will be cut to 1.1 million electrons since the transfer gate is merely a small section for the horizontal register.

Figure 13 Mean-Variance Plot Showing Charge Capacities of Various Structures Using a Kodak 24µm Pixel Device in Various Modes

|                                                                                            | Capacity In thousands of electrons | Low gain<br>(2μV/e <sup>-</sup> ) output | High gain<br>(10μV/e ̄) outpu |

|--------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------|-------------------------------|

| Charge capacity of a single pixel (Vertical CCD Register Capacity)                         | 650                                | 1.3 Volts                                | 2 Volts<br>(saturated)        |

| Horizontal CCD Capacity (Including H21/H22)                                                | 1100                               | 2.2 Volts                                | 2 Volts (saturated)           |

| Low Gain Amplifier and Floating Diffusion Capacity (Table 1&2 Settings)                    | 1900                               | 3.8 Volts                                | 2 Volts<br>(saturated)        |

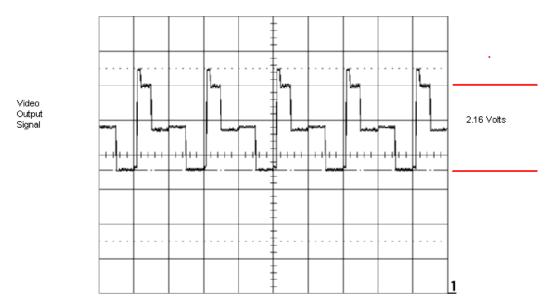

| Low Gain Amplifier and Floating Diffusion Capacity at nominal (KAF Specification) settings | 1080                               | 2.16 Volts                               | 2 Volts<br>(saturated)        |

| High Gain Amplifier and Floating Diffusion Capacity                                        | 200                                | Not Applicable                           | 2 Volts                       |

# Pixel Saturation: Adjusted CCD Settings

Figure 14 shows the Floating Diffusion charge capacity just before saturation with the sensor being operated in 2X2 Binning mode at the nominal values according to the device specification.

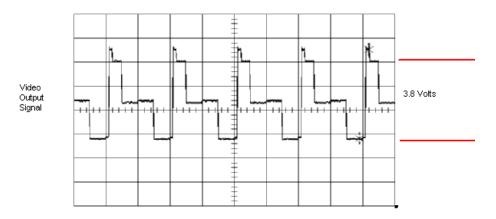

The floating diffusion output node capacity depends on several variables, namely VRD, VOG and the Reset clock. At the nominal settings suggested in the CCD performance specifications, the output node capacity, Qtot, is about the same as the Horizontal CCD capacity. In order to increase the charge capacity, Qtot, of

the floating diffusion output node, the floating diffusion well depth must be increased. This is achieved by making VOG less positive and making VRD more positive. The low level of the Reset clock must also be made less positive. When adjusting VRD more positive to 13.5 volts, VDD must me moved to 17 volts to maintain a linear behavior throughout a 3.8 volt dynamic range. In addition, VOG should be moved less positive to 3 volts and the low level of the Reset clock voltage swing should be lowered to 4 volts. These changes allow for a floating diffusion charge capacity of 1900000 electrons on  $24\mu m$  pixel devices.

Figure 14 Floating Diffusion Charge Capacity (Nominal Settings)

Figure 15 Floating Diffusion Capacity after VRD, VOG, Reset Adjustments

#### **Saturated Video Output Signal**

When operating a CCD in binning mode, particularly when using the floating diffusion, saturation can occur earlier than expected. This section outlines various early-saturation symptoms and methods for solving the problem.

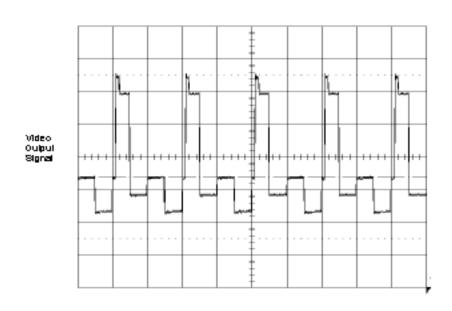

Charge is dumped onto the Floating Diffusion (FD) on the falling edge of H2. If enough electrons are present, they can flow back over the output gate if VOG is set too positive. Figure 16 illustrates the effect this has on the video output.

Figure 16 Output video when charge flows back over the output gate.

Figure 17 Charge Flowing back over VOG when the outhe floating diffusion capacity is reached.

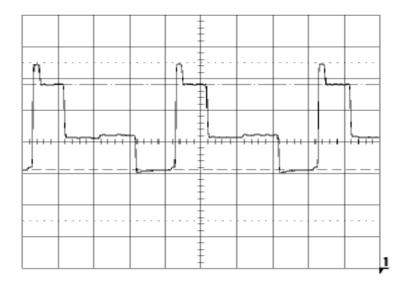

Another problem that can occur if enough electrons are present, is that they can flow over the Reset Gate if the low level of the Reset clock is not set low enough. Figure 18 illustrates the effect this has on the video output. Because the sensor is being uniformly illuminated, each of the two steps (pixels) in the waveform should be

approximately equal. The floating diffusion output node is saturated however, and electrons are being lost over the Reset Gate, and the second step can be seen to be less than the first step (see figure 19).

Figure 18 Charge lost over the Reset Gate

Figure 19 Charge lost over the Reset Gate

#### **Bias Recommendations when binning**

Based on the discussion presented in the last section, the standard operating voltages may be modified to create a larger output amplifier capacity. The tolerance on these voltages is reduced and may have to adjusted on an individual sensor basis.

The recommended CCD settings for operating Kodak's  $24\mu m$  Pixel Full Frame CCD sensors in binning applications are shown below. Bold type indicates possible deviation from the nominal setting in the Device Performance Specifications.

| Input Pin/s | DC Voltage (V |  |

|-------------|---------------|--|

| VRD         | 13.5          |  |

| VSS         | 2.0           |  |

| VDD         | 17.0          |  |

| VSUB        | 0.0           |  |

| VOG         | 4.0           |  |

| LOD/GAURD   | 10.0          |  |

Table 1: DC Operating Recommendations for Binning Operation

| Input Pin/s | Low Voltage (V) | High Voltage (V) |

|-------------|-----------------|------------------|

| V1          | -9.0            | 1.0              |

| V2          | -9.0            | 1.0              |

| H1          | -2.0            | 8.0              |

| H2          | -2.0            | 8.0              |

| H21         | -3.0            | 8.0              |

| H22         | -3.5            | -3.5             |

| Reset       | 4.0             | 10.0             |

**Table 2: AC Operating Recommendations for Binning Operation**

#### **Summary**

Kodak large pixel CCDs may be operated in binning by binning on the floating diffusion or by binning on the transfer gate. In addition to the timing requirements of the specific binning mode operation bias voltages need to be adjusted in order to achieve the maximum charge capacity at the output. The mode of operation and the output amplifier to be used may be determined by the demands for CCD sensitivity, noise, and dynamic range. While binning on the transfer gate provides for potential noise advantages over binning on the floating diffusion, the method has limited charge capacity compared to using the FD. In general Kodak large pixel CCDs provide the user with a high level of flexibility that allows each it to be tailored to meet the needs of many applications.

|                                                                                            | Capacity In thousands of electrons | Low gain<br>(2μV/e <sup>-</sup> ) output | High gain<br>(10μV/e <sup>-</sup> ) outpu |

|--------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------|-------------------------------------------|

| Charge capacity of a single pixel (Vertical CCD Register Capacity)                         | 650                                | 1.3 Volts                                | 2 Volts<br>(saturated)                    |

| Horizontal CCD Capacity<br>(Including H21/H22)                                             | 1100                               | 2.2 Volts                                | 2 Volts<br>(saturated)                    |

| Low Gain Amplifier and Floating Diffusion Capacity<br>(Table 1&2 Settings)                 | 1900                               | 3.8 Volts                                | 2 Volts<br>(saturated)                    |

| Low Gain Amplifier and Floating Diffusion Capacity at nominal (KAF Specification) settings | 1080                               | 2.16 Volts                               | 2 Volts<br>(saturated)                    |

| High Gain Amplifier and Floating Diffusion Capacity                                        | 200                                | Not Applicable                           | 2 Volts                                   |